復旦大學《集成電路設計導論》第一節 IC趨勢與學習資源導覽

《集成電路設計導論》是復旦大學微電子學院及相關專業的核心基礎課程,其第一節“IC趨勢”為學習者勾勒出了集成電路產業的宏觀藍圖與技術發展脈絡。本節不僅介紹了集成電路的歷史演進與當前熱點,更是理解未來芯片產業方向的關鍵入口。

一、集成電路(IC)的核心發展趨勢

本節課程重點探討了IC設計的幾大核心趨勢:

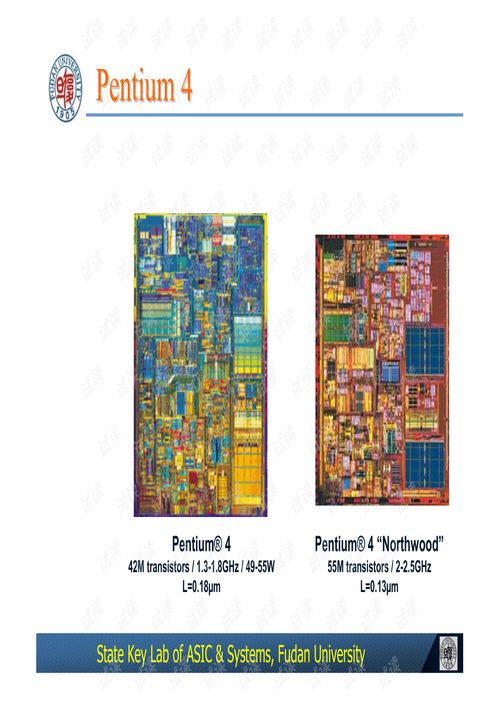

- 工藝制程的持續微縮:遵循摩爾定律,晶體管尺寸不斷縮小,集成度大幅提升,但隨之而來的物理極限與挑戰(如量子效應、功耗墻)已成為前沿研究的焦點。

- “超越摩爾”的多元化發展:在平面縮放趨緩的背景下,通過先進封裝(如Chiplet、SiP)、異構集成、新器件結構(如FinFET、GAAFET)以及新計算范式(如存算一體)來延續性能提升。

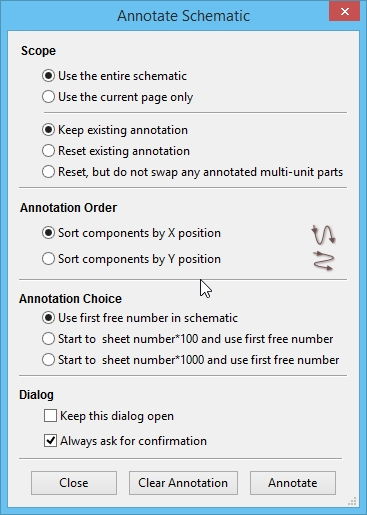

- 設計方法學的演進:隨著系統復雜度指數級增長,基于IP核的復用、高層次綜合(HLS)、以及借助人工智能的EDA工具,正成為提升設計效率、應對“設計生產率差距”的必由之路。

- 應用驅動的專業化:針對人工智能、自動駕駛、物聯網、高性能計算等不同應用場景,設計專用集成電路(ASIC)和領域特定架構(DSA)已成為提升能效與性能的關鍵。

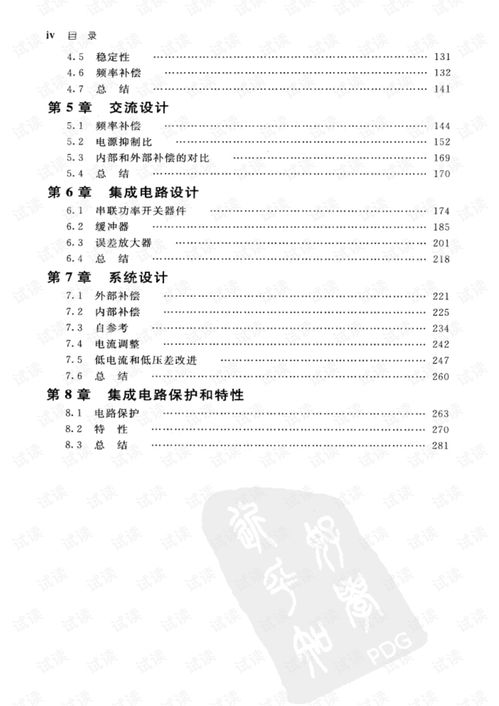

二、課程教程、筆記與習題資源

理論學習需與實踐鞏固相結合。圍繞該課程,學生通常會整理和尋求以下資源:

- 課程教程與課件:復旦大學的官方課件是知識框架的基礎,系統闡述了基本概念、技術節點和趨勢分析。

- 學習筆記:詳實的課堂筆記或知識梳理筆記,有助于提煉重點、消化難點,形成個人化的知識體系。

- 課后習題與解析:通過完成習題,可以檢驗對工藝趨勢、性能評估、設計挑戰等概念的理解程度,是鞏固學習成果的重要環節。

三、代碼類與其它實踐資源(以CSDN等平臺為例)

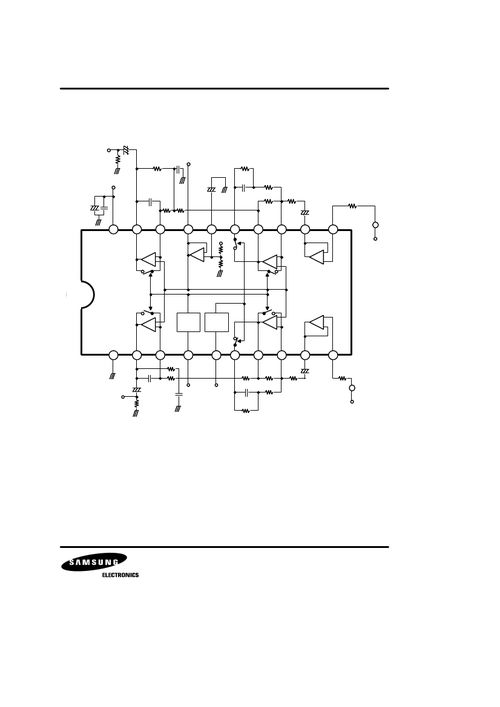

集成電路設計不僅是理論學科,更是實踐工程。入門階段常涉及硬件描述語言和EDA工具的使用。

- 代碼類資源:在CSDN、GitHub等開發者社區,可以找到與課程配套或相關的實踐項目代碼,例如:

- Verilog/VHDL基礎代碼:組合邏輯、時序邏輯、狀態機等經典數字電路模塊的實現。

- 簡單項目實例:如ALU(算術邏輯單元)、FIFO、計數器等的設計與仿真代碼。

- EDA工具腳本:用于綜合、布局布線的Tcl腳本示例。

- 使用建議:下載使用這些資源時,應重在理解其設計思路與實現方法,而非簡單復制。建議結合課程理論,自行嘗試編寫、仿真并調試代碼,以真正掌握設計流程。

- 其它資源:還包括開源EDA工具(如Verilator、GTKWave)、FPGA開發板入門教程、產業分析報告等,這些都能幫助構建從理論到產業的全景認知。

四、學習路徑建議

- 夯實基礎:以課程教材和課件為核心,深入理解IC制造流程、MOS管原理和數字設計基礎。

- 跟蹤趨勢:結合第一節內容,主動關注半導體行業資訊、頂級會議(如ISSCC、VLSI)論文,了解最前沿的技術動向。

- 動手實踐:盡快開始學習Verilog等硬件描述語言,使用EDA工具進行簡單的數字電路設計、仿真和綜合,將理論轉化為工程能力。

- 利用社區:合理利用CSDN、知乎、開源中國等平臺上的技術博客和資源,但需注意甄別信息質量,并以官方資料和經典教材為最終依據。

復旦大學《集成電路設計導論》的第一節為我們打開了一扇大門,其內容貫穿了集成電路的過去、現在與未來。高效的學習方法在于將系統的課程理論、前沿的趨勢洞察與扎實的動手實踐緊密結合,從而為成為一名優秀的集成電路設計工程師奠定堅實的基礎。

如若轉載,請注明出處:http://m.beautylighting.com.cn/product/5.html

更新時間:2026-03-29 09:07:07